International Journal of Engineering Research-Online A Peer Reviewed International Journal Articles available online http://www.ijoer.in

Vol.3., Issue.4., 2015 (July-Aug)

# **RESEARCH ARTICLE**

# ISSN: 2321-7758

# DESIGN A LOW POWER MICROPROCESSOR USING CLOCK GATING TECHNIQUE

# SAURABH H SHAH<sup>1</sup>, AMIT KUMAR<sup>2</sup>, RAVI BUTANI<sup>3</sup>

<sup>1</sup> Scholar, Marwadi Education Foundations of Group of Institute, Rajkot, Gujarat, INDIA <sup>2,3</sup> Assistant Professor, Department of Electronics and Communication, MEFGI, Rajkot, Gujarat, INDIA

**SAURABH H SHAH**

**RAVI BUTANI**

## **AMIT KUMAR**

#### INTRODUCTION

As technology is shrinking and high performance is require, power dissipation is major issue for portable devices. Nowadays most of the devices are portable devices, so very low amount of power dissipation play major role in devices.

Power is an amount of energy consumed by devices per unit time<sup>[14]</sup>. Power is inversely proportional to the performance in term of speed. But for low power design, performance is bottleneck. So if power dissipation is less, performance will be increase.

Power dissipation means power which is dissipated in term of heat in devices<sup>[6]</sup>. There are two

## ABSTRACT

In today's era technology is scaling down rapidly and market demanding for the low power and high performance digital circuits like microprocessor. Scaling of supply voltage is limit the speed of the design and will lead to setup and hold time violation. Clock gating is effective technique which can be used to save 3 to 6% of total power. In this paper Microprocessor is implemented using Altera Quartus II tool and the logic of Clock gating is applying on datapath block. Total power dissipation is reduced by 20% of dynamic power.

Key Words -- microprocessor, power, dynamic power dissipation, clock gating.

**©KY PUBLICATIONS**

type of power dissipation in microprocessor. Those are Static and dynamic power dissipation. Static power can be known as leakage power, dynamic power is switching power as well as shirt circuit power<sup>[6]</sup>.

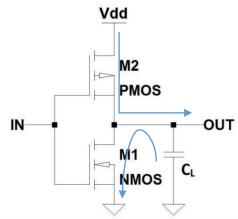

For dynamic power dissipation there are two components one is switching power due to charging and discharging of load capacitance. The other is the short circuit power due to the nonzero rise and fall time of input waveforms. The switching power of a single gate can be expressed as<sup>[6]</sup>

$$P_D = \alpha C_L V_{DD}^2 f \qquad 1$$

Where  $\alpha$  is the switching activity, f is operation frequency,

$C_L$  is the load capacitance,

$V_{DD}$  is the supply voltage.

## Figure 1 Dynamic Power dissipation<sup>[6]</sup> Introduction of Microprocessor

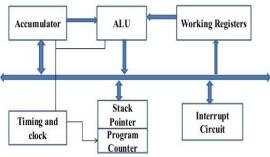

It is controlling unit of portable devices, which is implemented on very small chip. It is a multipurpose, programmable device that accepts digital data as an input, processes it according to instructions stored in its memory, and provides results as output<sup>[13]</sup>. The basic block diagram of it is shown in below figure.

**Figure 2 Block diagram of microprocessor**<sup>[7]</sup> Microprocessor has mainly four units<sup>[7]</sup>,

- data path unit

- control unit

- machine unit

- interface unit

## **Clock Gating**

Microprocessor is working on a clock, which is globally distributed in it. Clock play important role in microprocessor because this is the only component which is continuously switching<sup>[4]</sup>. So if we reduce the switching power of clock, we can also improve the power of microprocessor<sup>[11]</sup>.

One signal is introduced here, that is clk-

control signal. Clock gating means clock is ANDed with clk-control signal, when input data is in ideal stage<sup>[5]</sup>. Clock gating technique is mainly applied on sequential circuit, dynamic circuits<sup>[3][9]</sup>.

For effective clock gating three things mainly  $considering^{[1]}$ ,

1. Which circuit is gated?

If selected circuit is mostly active circuit, then it is worthless.

2. When circuits is gated?

In every circuit, one signal is taken place, which is known as predictor circuit. This is use for prediction, when input is arrived and when it becomes zero, so clock signal become gated over there.

3. How much period of time it will be gated? Predictor circuit is take part for this too. It use for observation of input of gated circuit. When any input is assigned, then time period break and circuit run continuously.

## **Types of Clock Gating**

Predictor circuit is design using two methods those are

- Latch free clock gating

- Latched clock gating

These both techniques have its own advantages and disadvantages. Let's start with latch free clock gating.

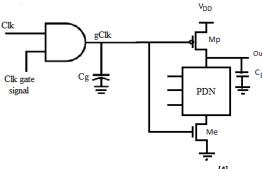

• Latch free clock gating

Clock gating is applied using different gates and latches. When clock is gated using gates like AND or OR gates, it is known as latch free clock gating<sup>[4]</sup>. But it has one disadvantage, glitch is generated over here. Glitch means unwanted signal, which is affect whole operation. For reducing the reducing the glitch effect OR gate must be work in active low region and AND gate is work in active high region.

## Figure 3 latch free clock gating<sup>[4]</sup>

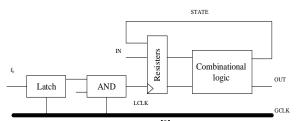

Latched clock gating

To overcome the disadvantage of latch free clock gating one new technique is introduced. In this technique, latches are used just before AND gate. Latch is working on positive edge of clock<sup>[3][12]</sup>.

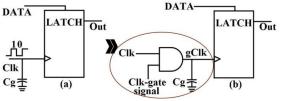

Figure 4 latched clock gating<sup>[3]</sup> Principle of clock gating

The clock network in a microprocessor feeds the clock to sequential elements like flip-flops and latches, and to dynamic logic gates<sup>[1][2][8]</sup>.

At a high level, gating the clock to a latch or a logic gate by ANDing the clock with a control signal prevents the unnecessary charging/discharging of the capacitances when the circuit is idle, and saves the circuit's clock power<sup>[2][10]</sup>. Figure (a) shows the schematic of a latch element.

Figure 5 clock gating technique<sup>[1]</sup>

$C_g$  is the latch's cumulative gate capacitance connected to the clock. Due to clock switches every cycle,  $C_g$  performs charging and discharging operation in every cycle and consumes the significant amount of power. The latch still consumes clock power, even if the inputs do not change from one clock ti next.

In figure (b), the clock is gated by ANDing it with a control signal, which we refer as *Clk-gate signal*<sup>[1]</sup>. When the latch is not required to switch state, Clk-gate signal is turned off and the clock is not allowed to charge/discharge C, saving clock power. Because the latches of an operand can be driven by an AND gate, the capacitance of the AND gate itself is much smaller than the sum of multiple C<sub>g</sub> of these latches. Hence, we can get a net power saving. **Simulations And Results**

Simulation start with design of microprocessor. The microprocessor is design using Verilog code. The features of microprocessor

- 100 instructions for operation

- 64K byte memory addressing capacity

- Eight addressing mode

- 16-bit ALU with bit, byte and BCD operations

- Fully synchronous design

- Uniform two clock cycle

Next step of simulation is verification and measurement of power dissipation. This process is done using Altera quartus II. Coding part is done in verilog HDL. Here we mainly measure the power dissipation of microprocessor in normal mode and in clock gated mode. For measurement of power dissipation, we used powerplay power analyzer tool, which is part of Altera Quartus II.

The result is shown in below table. Table shows the total power dissipation, dynamic power dissipation, static power dissipation and IO power dissipation. The changes in dynamic power is measurable for microprocessor.

| TABLE 1: COMPARISON OF POWER DISSIPATION |         |         |         |        |

|------------------------------------------|---------|---------|---------|--------|

| Mode                                     | Total   | Dynamic | Static  | 10     |

|                                          | power   | power   | power   | power  |

| Normal                                   | 87.80mW | 0.10mW  | 81.35mW | 6.35mW |

| Clock                                    | 87.69mW | 0.02mW  | 81.35mW | 6.32mW |

| Gating                                   |         |         |         |        |

## CONCLUSION

In this paper, microprocessor is design using Verilog HDL in Altera Quartus II tool. Clock gating is applied a datapath using Verilog. The microprocessor which is operated in normal mode, dynamic power dissipation is 0.10mW. When Clock Gating (CG) is applied power is reduced by 0.02mW. Total dynamic power is reduced by 20%.

## REFERENCES

- [1] H. li, S.Bhunia, Y. Chen, K.Roy, "DCG: Deterministic Clock Gating for Low Power Microprocessor," IEEE Trans. Very Large Scale Integr, (VLSI) Syst, VOL-12, NO.3, MARCH 2004, pp. 245–254.

- [2] J.Ravindra, T. Anuradha, "Design of low power RISC Processor by Applying clock gating technique", International Journal of Engineering Research and Applications(IJERA), Vol.2, Issue 3, May-jun 2012, pp. 94-99.

- [3] J. Carlsson, K. Palmkvist, "A clock Gating for Globally Asynchronous Locally Synchronous Systems", Department of Electrical Engineering,

Linkopings universitet SE-58183, Linkopings Sweden, unpublished.

- [4] S. Huda, M. Mallick, J. Anderson, "Clock Gating Architecture for FPGA Power Reduction", Department of ECE, University of Toronto, unpublished.

- [5] M. Kamaraju, G. Chinavenkateswararao, "Low Power Reduced most Instruction Set Architecture using Clock Gating Technique", International Journal of VLSI design & Communication Sysytem, Vol. 4, No. 5, October 2013, pp.35-51.

- [6] G. Yeap. "Introduction", in Practical Low Power Digital VLSI Design, Published by Springer Science + Business Media, LCC, 1998, ch 1,pp. 1-26.

- [7] R. Gaonkar, "Microprocessor, Microcomputer and Assembly Language", in Microprocessor Architecture, Programing and Applications with the 8085, published by Penram International Publishing, 2010, ch1, pp 3-30.

- [8] A. Chandrakasan, R. Brodersen, "Low Power Digital CMOS Design", Springer Science+Business Media, LLC, 1995

- [9] Q. Wu, M. Pedram, X. Wu, "Clock-Gating and Its Application to Low Power Design of Sequential Circuits", IEEE Transactions on Circuits and Systems-I: Fundamental Theory and Applications, Vol.47, No. 103, March 2000, pp. 415-420.

- [10] M. Donno, A. Ivaldi, L. Benini, E. Macii, "Clock-Tree Power Optimization based on RTL Clock-Gating", BullDASTs.r.l., Torino, Italy, unpublished.

- [11] J. Oh, M. Pedram, "Gated Clock Routing for Low Power Microprocessor Design", IEEE Transactions on Computer-Added Design of Integrated Circuits and Systems, Vol. 20, No. 6, June 2001, pp. 715-722.

- [12] S. Winner, I. Koren, "Design Flow for Flip-Flop Grouping in Data-Driven Clock Gating", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No.4, April 2014, pp. 771-778.

- [13] R. Kaur, Anuj, "8 bit RISC Processor Using Verilog HDL", International Journal of Engineering Research and Applications, ISSN: 2248-9622, Vol. 4, Issue 3, march 2014, pp-417-422.

[14] http://www.answers.com/Q/What\_is\_Power\_di ssipation

#### About authors

Saurabh H Shah has completed bachelor of Engineering (Electronics and Communication Engineering) from R.K.College of Engineering and Technology, Rajkot, Gujarat, India in 2013. Now he is Pursuing Masters of Engineering (VLSI System Design) from Marwadi Education Group of Institutions, Rajkot, Gujarat, India.

**Ravi Butani** is currently working as an Assistant Professor in Marwadi Education Foundation's Group of Institutions, Rajkot, Gujarat, India. He has completed M.E. in Communication Systems Engineering from L.D. College of Engineering, Ahmedabad in 2011. He has completed B.E. in Electronics and Communication from Vishwakarma Government Engineering College of Engineering, Gandhinagar in 2007.

**Amit Kumar** is currently working as an Assistant Professor in Marwadi Education Foundation's Group of Institutions, Rajkot, Gujarat, India. He has completed M.Tech in VLSI Design from Malaviya National Institute of Technology in 2012. He has completed B.E. in Electronics and Communication from Government Engineering College, Rajkot in 2009.